Using NL3W (Netlist utility for BSch3V)

NL3W generates the netlist, from BSch3V's schematic file.

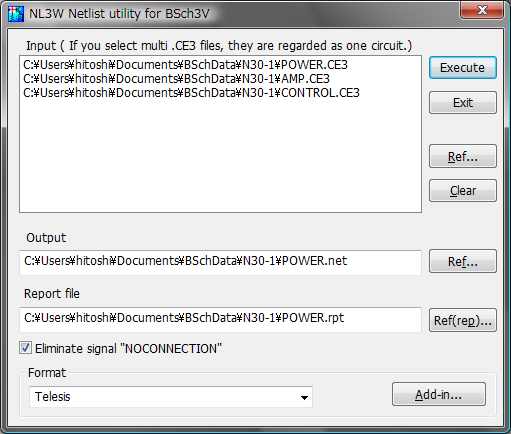

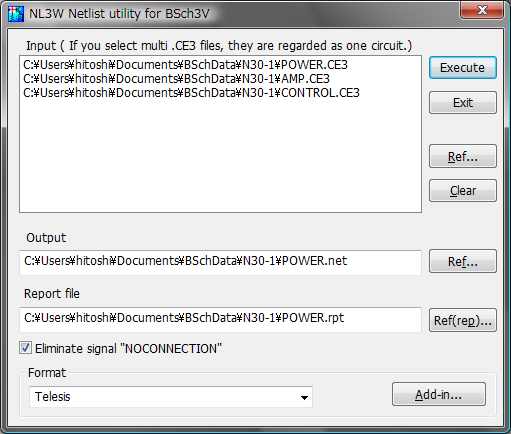

Operation

- Start up NL3W

- Select the input schematic file(s).

There are 2 ways to select input file(s).

- Click the "Ref..." button on right side of the "Input" listbox.

- Drag and drop from Explorer.

The output file name is automaticaly created.

- Format

You can select "Telesis" or "Protel" format by default.

BSch3V package includes "PADS" add-in as a sample.(with source

code)

To Create a netlist with PADS format, Click [Add-in] and select nl3wpads.dll.

- Click the "Execute" button.

Rules

- Ignored object

NL3W ignores comment, dash-line, bus-line, bus-entry, and wire-entry.

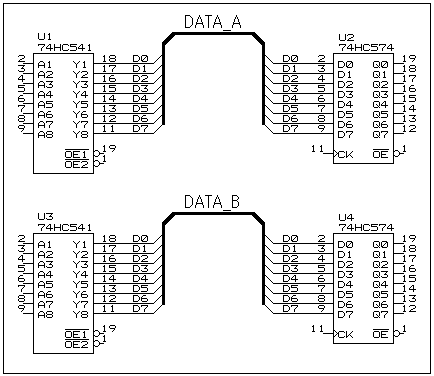

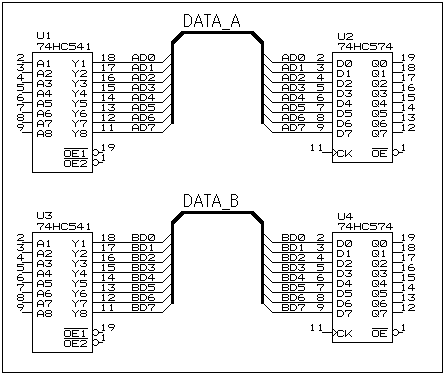

If you draw the schematic like the following figure, NL3W doesn't work

as intended.

In this case, the signal D0 is connected to U1.18, U2.2, U3.18, and U4.2

by NL3W.

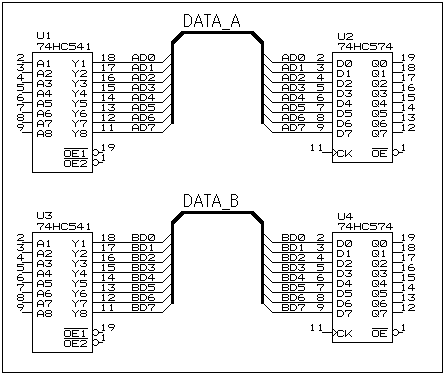

To avoid the such trouble, you should draw , as shown in the following

figure.

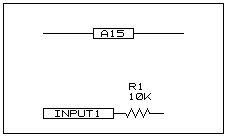

- Name of Signal line

Signal lines can be named.

The signal lines which have the same name are connected by NL3W.

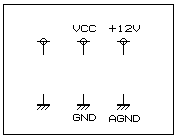

- Tag

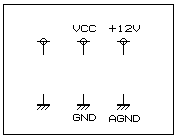

- Sigle-pin component

- The single-pin component with reference number has no effect.

- If the single-pin component has no value, signal line is named with original

name.

- If the single-pin component has value(like "GND", "+12V"),

signal line is named with the value.

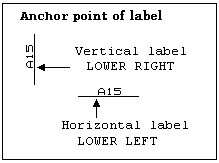

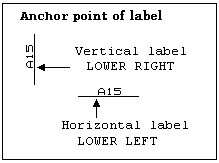

- Label

The vertical(horizontal) label names the signal name of vertical(horizontal)

line.

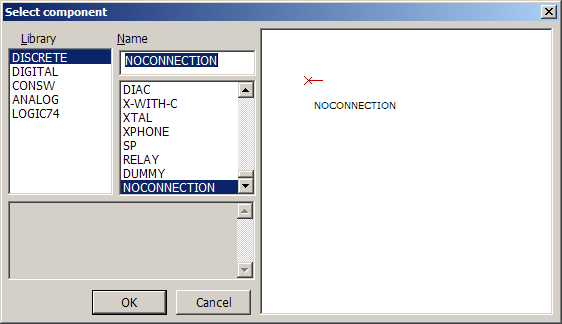

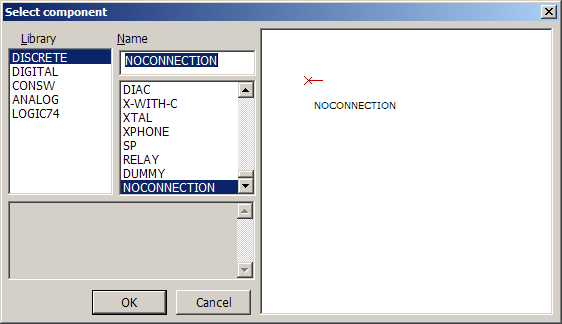

- Eliminate signal NOCONNECTION

If you check this option, NL3W does not output net that has a signal name

"NOCCONECTION".

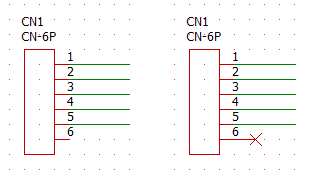

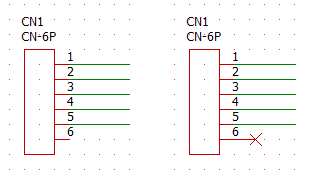

There is a component "NOCONNECTION" in the standard library "DISCRETE".

It shows that the terminal is connected nowhere explicitly.

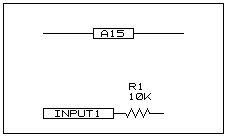

Left: Non-explicit NO CONNECTION

Right: Explicit NO CONNECTION

If you use the component "NOCONNECTION" and make netlist with

NL3W, you have to check this option.

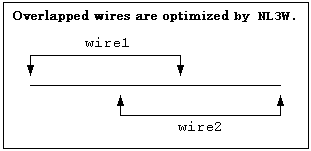

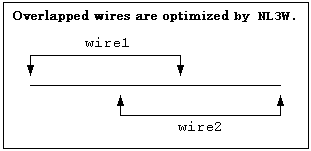

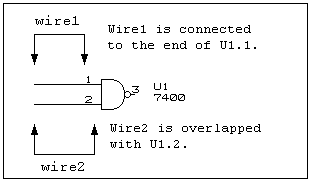

- Optimizing overlapped wires

If overlapped wires are vertical or horizontal, they are regarded as a

single wire by NL3W.

Current version of BSch3V optimizes overlapped horizontal and vertical

wire automatically.

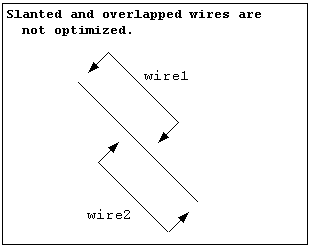

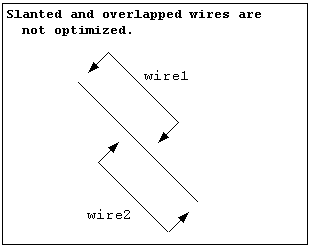

But slanted wires are not optimized. So if their end are not located at

the same position, They are regarded as unconnected lines.

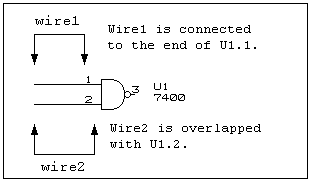

And overlapping of wire and pin is not optimized.

Wire2 is not connected to U1.2 in the netlist.